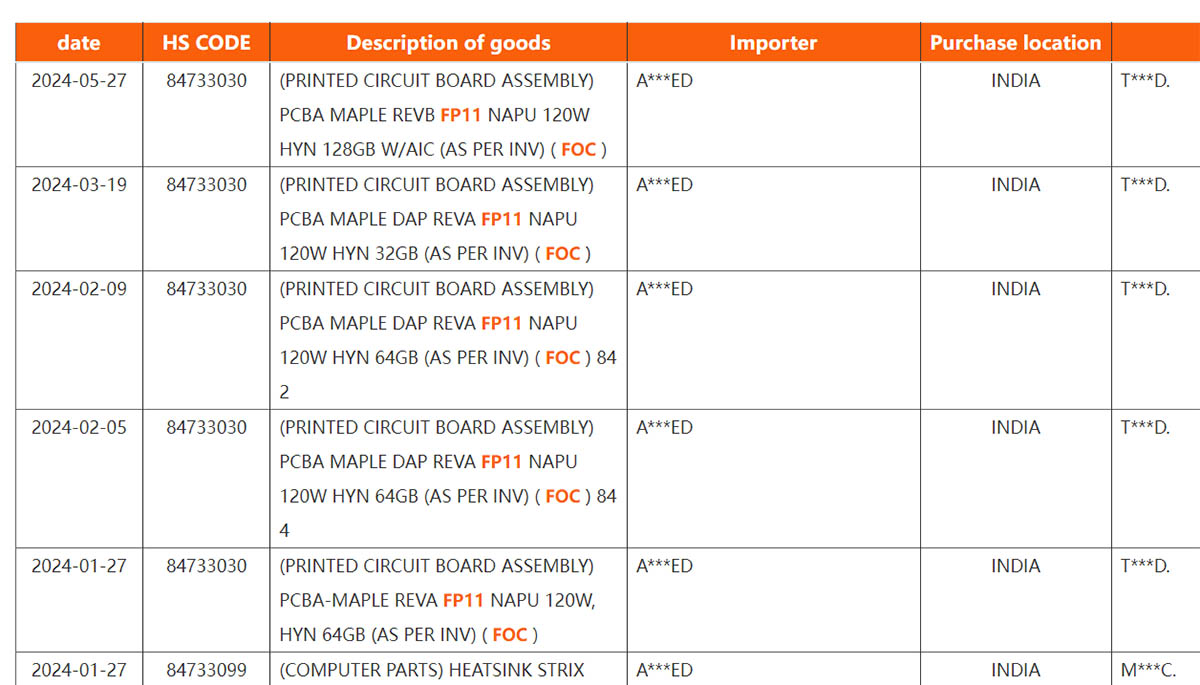

AMD hat auf der Computex Taipei 2024 den auf der Zen-5-Architektur basierenden Desktop-Prozessor Riptide 9000, Granite Ridge, und den mobilen Prozessor Riptide AI 300, Strix Point, vorgestellt. Es wurde jedoch auch eine sehr wichtige APU, der Strix Halo, vorgestellt, die in den Versandlisten des Zolls Aufmerksamkeit erregt hat. Berichte bestätigen, dass diese APU eine TDP von ungefähr 120W hat und mit mindestens 32GB RAM ausgestattet ist.

Laut der NewBid Data Website wurde kürzlich eine neue Lieferung von Maple Rev.B PCBs verschickt. Diese Lieferung dient als FP11-Sockel Strix Halo-Referenzplattform, die AMD für seine jüngsten Tests verwendet hat und die mit Speicherkapazitäten von bis zu 128 GB aufwartet. Frühere Testplattformen hatten 32 GB und 64 GB Speicher. Durchgesickerte Dokumente zeigen, dass der Strix Halo einen 256-Bit-Speicherbus und LPDDR5-8000-Speicher unterstützt. Bemerkenswert ist, dass diese APU den Speicher nicht in die CPU integriert - angesichts der Tatsache, dass aktuelle LPDDR5X-Einzelchips maximal 16 GB groß sind, erfordert die Konfiguration mindestens acht Speicherchips rund um die CPU.

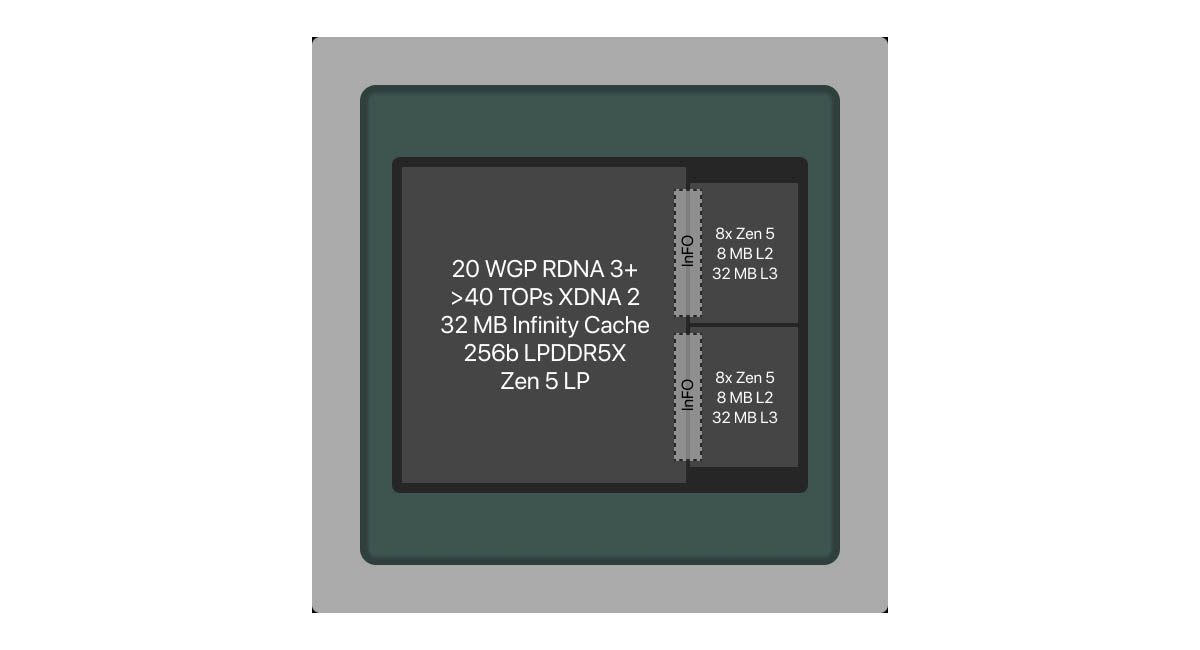

Die umfangreiche Speicherzuweisung ist vermutlich für die Ausführung umfangreicher KI-Modelle gedacht, die bekanntermaßen sehr speicherintensiv sind. Von der Strix Halo selbst wird eine starke KI-Leistung erwartet. Sie nutzt ein MCM-Design mit drei Chips - zwei CCDs und einem GCD. Jeder Kern der Zen-5-Architektur verfügt über einen 1 MB großen L2-Cache, wobei jeder CCD 8 Kerne und einen 32 MB großen L3-Cache beherbergt. Daraus ergeben sich insgesamt 16 MB L2-Cache und 64 MB L3-Cache, wobei die beiden CCDs über den IF-Bus miteinander verbunden sind.

Der IOD wurde durch den GCD ersetzt, der im Wesentlichen ein IOD mit größeren integrierten Kernen ist. Der GCD hat eine größere Chipfläche als die beiden CCDs und verfügt über eine NPU der XDNA-2-Architektur mit einer Rechenleistung von mehr als 40 TOPS. Zusätzlich ist eine RDNA3+-Architektur-GPU mit 40 CUs integriert und ein 32 MB MALL-Cache, um mögliche Defizite bei der Speicherbandbreite zu beheben.