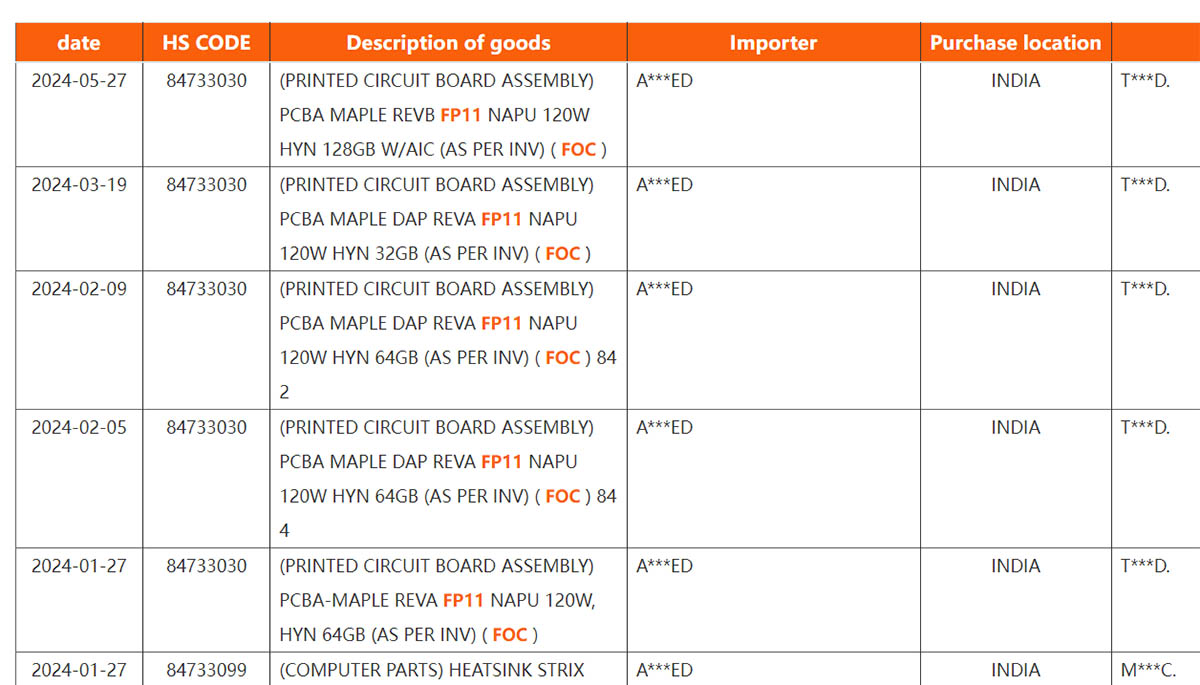

AMDはCOMPUTEX TAIPEI 2024で、Zen 5アーキテクチャベースのRiptide 9000デスクトップ・プロセッサー「Granite Ridge」とRiptide AI 300モバイル・プロセッサー「Strix Point」を発表しました。しかし、税関の出荷リストで注目されている非常に重要なAPU「Strix Halo」も発表されました。報告によると、このAPUのTDPは約120Wで、少なくとも32GBのRAMが搭載されていることが確認されています。

NewBid Dataのウェブサイトによると、Maple Rev.B PCBの新しい出荷が最近行われました。この出荷は、AMDが最近のテストに使用しているFP11ソケットのStrix Haloリファレンス・プラットフォームとなり、最大128GBのメモリ性能を誇ります。以前のテスト・プラットフォームは32GBと64GBのメモリを搭載していました。リークされた文書によると、Strix Haloは256ビットのメモリバスとLPDDR5-8000メモリをサポートしています。現在のLPDDR5Xシングルチップの最大容量が16GBであることを考えると、この構成にはCPUを取り囲む少なくとも8つのメモリチップが必要となります。

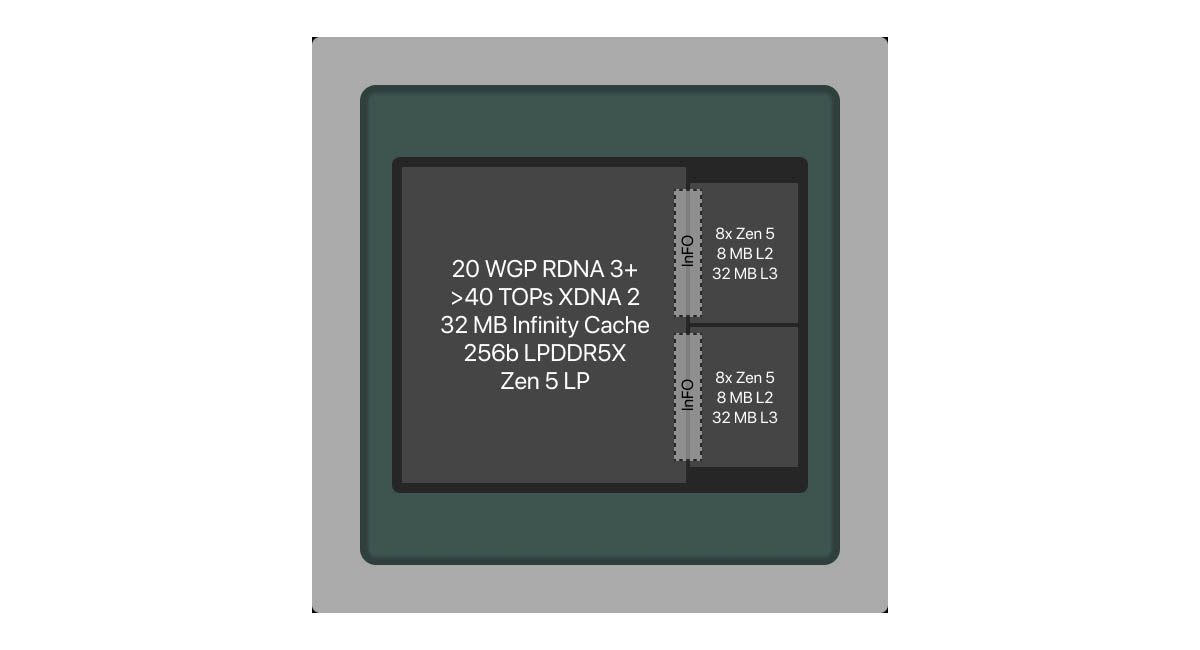

この大幅なメモリ割り当ては、メモリを大量に消費することで知られる大規模なAIモデルを実行するために設計されたと推測されます。Strix Haloは、3つのチップ(2つのCCDと1つのGCD)からなるMCM設計を採用し、強力なAI性能を発揮すると期待されています。Zen 5アーキテクチャの各コアには1MBのL2キャッシュが搭載され、各CCDには8コアと32MBのL3キャッシュが搭載されています。この結果、合計16MBのL2キャッシュと64MBのL3キャッシュを搭載し、2つのCCDはIFバスで相互接続されています。

IODはGCDに取って代わり、本質的にはより実質的な統合コアを備えたIODとなります。GCDは、2つのCCDよりもチップ面積が大きく、40TOPS以上の演算能力を持つXDNA 2アーキテクチャのNPUを搭載しています。さらに、40CUのRDNA3+アーキテクチャGPUも統合し、潜在的なメモリ帯域幅の不足に対処するために32MBのMALLキャッシュを備えています。