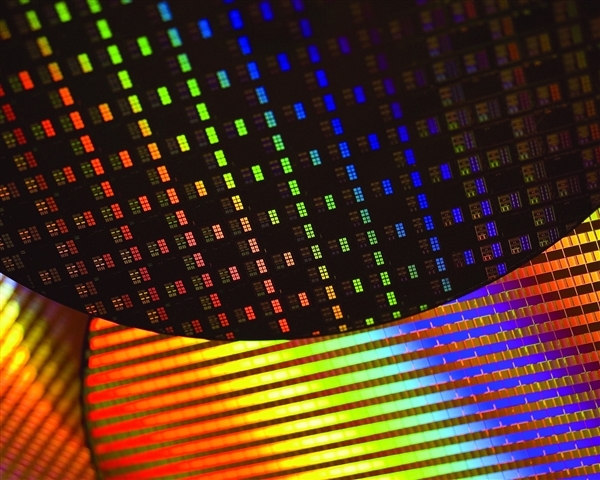

メディアの報道によると、TSMCは完全なバックサイド・パワー・デリバリ・ネットワーク(BSPDN)ソリューションを提案しているが、実装は複雑でコストがかかり、2026年に量産される見込みである。

現在、優れた性能と効率で知られるTSMCのスーパー・パワー・レール・アーキテクチャへの依存は、ハイパフォーマンス・コンピューティング(HPC)製品の複雑な信号伝送と集中的な電力供給のニーズに対する効果的なソリューションとして業界で認められている。

このアーキテクチャは間もなくA16プロセスで大規模に採用される予定で、半導体性能とエネルギー効率の大幅な飛躍を予告している。スーパーレール・アーキテクチャーは、従来のN2Pプロセスと比較して、同じ動作電圧で最大8~10%の性能向上を実現する。逆に、同じ速度を維持しながら消費電力を15~20%大幅に削減し、1.1倍の集積度向上を実現する。

バックサイド電源技術の実装は、一連の重要な技術的ブレークスルーに依存していることは注目に値する。中でも最も重要なのは、チップの裏面をトランジスタと密着するのに十分な厚さまで精密に研磨することである。

この課題に対し、TSMCは、表側研磨後にキャリアウェハを接合する技術を巧みに導入し、その後の裏面製造工程をしっかりと支え、スムーズな進行を実現した。

さらに、ナノシリコンスルーホール(nTSV)などの最先端技術を取り入れることで、装置の精度やプロセス制御への要求も高まっている。ナノスケールのビア内に銅金属を均一に蒸着させるために、TSMCはこの精密で複雑な製造工程をサポートするため、よりハイエンドの設備に投資する必要がある。

TSMCのスーパーレールアーキテクチャーの段階的な量産化により、半導体の性能とエネルギー効率における競争の新たなラウンドをリードするだけでなく、サプライチェーン全体の上流と下流の相乗的な発展を促進し、業界全体に力強い成長の勢いを注入することになるでしょう。