언론 보도에 따르면 TSMC는 구현이 복잡하고 비용이 많이 들지만 완벽한 백사이드 전력 공급 네트워크(BSPDN) 솔루션을 제안했으며, 2026년에 양산될 것으로 예상됩니다.

현재 TSMC의 슈퍼 파워 레일 아키텍처는 뛰어난 성능과 효율성으로 업계에서 고성능 컴퓨팅(HPC) 제품의 복잡한 신호 전송과 집중적인 전력 공급 요구에 대한 효과적인 솔루션으로 인정받고 있습니다.

이 아키텍처는 곧 A16 공정에 대규모로 채택되어 반도체 성능과 에너지 효율의 획기적인 도약을 예고하고 있습니다. 기존 N2P 공정에 비해 슈퍼 레일 아키텍처는 동일한 작동 전압에서 최대 8~10%의 성능 향상을 제공합니다. 반대로, 동일한 속도를 유지하면서 전력 소비를 15~20% 크게 줄이고 1.1배의 집적도 증가를 실현합니다.

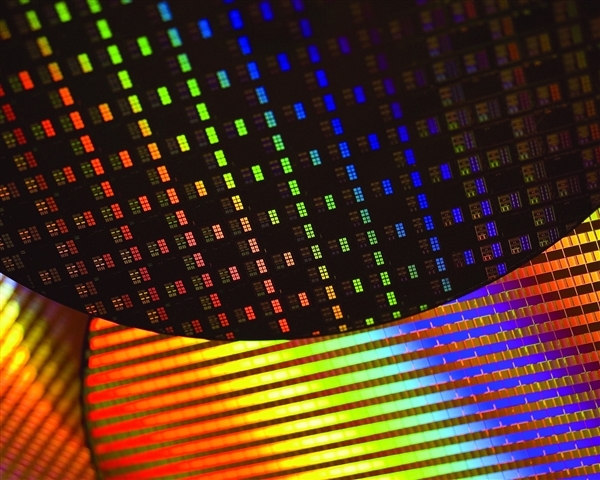

백사이드 전원 공급 기술의 구현은 일련의 주요 기술 혁신에 의존한다는 점에 주목할 필요가 있습니다. 그중 가장 중요한 것은 칩의 뒷면을 트랜지스터와 밀착할 수 있는 두께로 미세 연마하는 것인데, 이 공정은 미묘하지만 웨이퍼의 기계적 강도를 필연적으로 약화시킬 수밖에 없습니다.

이 과제를 해결하기 위해 TSMC는 앞면 연마 후 캐리어 웨이퍼 본딩 기술을 능숙하게 도입하여 후속 뒷면 제조 공정을 견고하게 지원하고 원활한 진행을 보장합니다.

또한 나노 실리콘 관통 홀(nTSV)과 같은 최첨단 기술의 통합으로 장비 정밀도 및 공정 제어에 대한 요구가 더욱 높아졌습니다. 나노 크기의 비아 내에 구리 금속을 균일하게 증착하기 위해 TSMC는 이 정밀하고 복잡한 제조 공정을 지원하기 위해 더 많은 고급 장비에 투자해야 합니다.

TSMC의 슈퍼 레일 아키텍처가 점진적으로 양산됨에 따라 반도체 성능과 에너지 효율의 새로운 경쟁을 주도할 뿐만 아니라 업스트림 및 다운스트림 전체 공급망의 시너지 개발을 촉진하여 업계 전체에 강력한 성장 모멘텀을 불어넣을 것입니다.