インテルは、18 Aプロセス (1.8ナノ相当) が順調に進んでおり、予想を上回る進捗を見せていると発表しました。これにより、Arrow Lakeプロセッサの20 Aプロセス (2 NM相当) バージョンはキャンセルされ、外部の代替工場 (TSMC) が使用されることとなりました。

一部報道によると、博通はインテルの18 Aプロセスをテストしているものの、結果は楽観的ではなく、代理工場としての協力をキャンセルする可能性があるとされています。

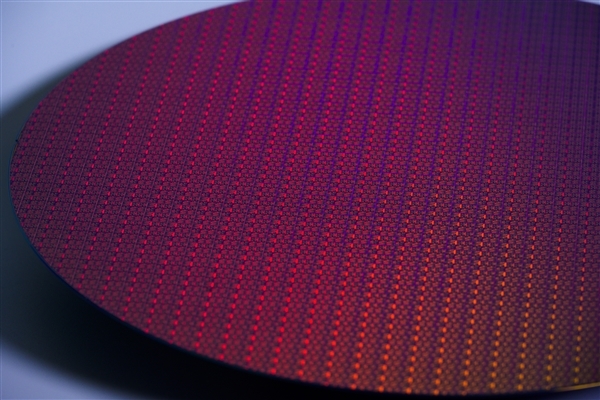

ドイツ銀行2024技術大会で、インテルのパット・ガイシンジャー最高経営責任者は「この段階で、18 Aプロセスの欠陥密度 (D0) が0.4未満であることを非常に興奮してお伝えします」と述べました。

欠陥密度とは、ウェハー1平方センチメートルあたりの欠陥数を指します。一般に0.5未満が良好だと考えられています。もし18 Aプロセスが実際に0.4未満の成績を収めているならば、それは非常に印象的です。

特に、この数四半期で18 Aが量産に入ることを考慮すれば、その欠陥密度はさらに低下することが期待されます。

参考として、N7 (7 nm) およびN5 (5 nm) のいずれも、量産前の3四半期の欠陥密度は約0.33であり、後者は量産時に0.1に低下しました。しかし、前者は量産において依然として比較的高い欠陥密度を示し、0.1に低下するのに数四半期を要しました。

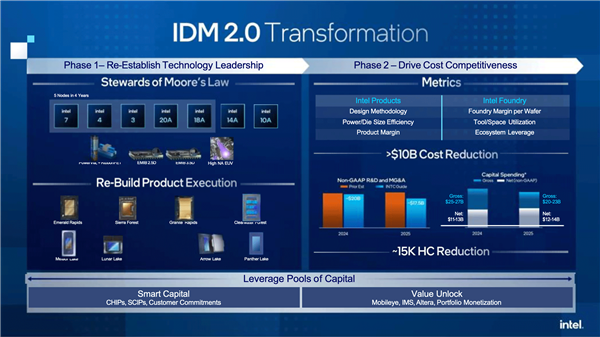

インテルの初の18 Aプロセスを使用した消費者向け製品はPanther Lakeで、Core Ultra 300シリーズとしてリリースされる予定です。最初のデータセンター向け製品はClearwater Forestで、Xeon Ultraシリーズとしてリリース予定です。どちらの製品も量産段階にあり、2025年に発表される予定です。

18 Aプロセスはインテルがプロセス技術面でTSMCを超えるための重要な一歩であり、外部の代替工場に提供するための重要な機会でもあります。

インテルは、マイクロソフトや米国防総省などの潜在的な顧客が非常に興味を持っていることを明かしました。2025年までに、インテル自身の製品と外部顧客の製品を含む8つの18 Aチップが完成する予定です。