인텔은 18A 공정(1.8나노당량)이 기대 이상으로 순조롭게 진행되고 있다고 발표했습니다. 이에 따라 Arrow Lake 프로세서의 20A 공정(2 NM에 해당) 버전이 취소되고 외부 대공장(TSMC)으로 전환되었습니다. 브로드컴이 인텔 18A 공정을 테스트하고 있지만 결과가 녹록지 않아 파운드리 협력을 취소할 수도 있다는 보도가 나왔습니다.

도이치뱅크 2024 기술 컨퍼런스에서 인텔 CEO 팻 게일싱어는 "이 단계에서 18A 공정의 결함 밀도(D0)가 0.4 미만으로 매우 건강하다는 사실을 알려드리게 되어 매우 흥분됩니다."

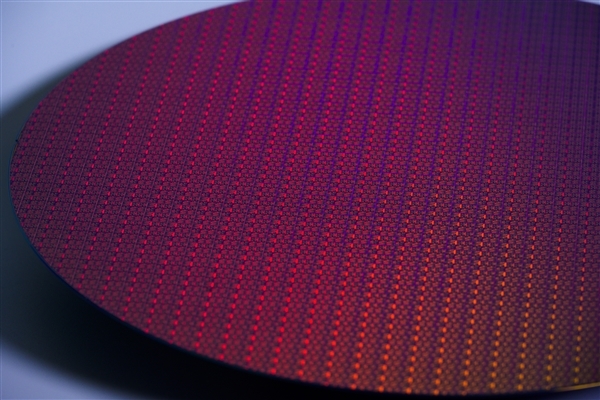

결함 밀도는 제곱 센티미터당 웨이퍼 슬라이스의 결점 수를 나타냅니다. 일반적으로 0.5 미만은 좋은 것으로 간주됩니다. 18A 프로세스가 확실히 0.4 미만의 성적을 냈다면 상당히 인상적입니다.

특히 몇 분기만 더 지나면 18A가 양산에 들어간다는 점을 감안하면 그 결함 밀도는 여지없이 더 낮아질 것입니다.

대적전 N7 7 nm와 N5 5 nm는 양산 시 0.1로 감소하는 양산의 처음 3분기의 결함 밀도가 약 0.33입니다. 그러나 전자는 양산에서 상대적으로 높은 결함 밀도를 계속 갖고 있으며 이를 0.1로 낮추는 데 몇 분기가 걸렸습니다.

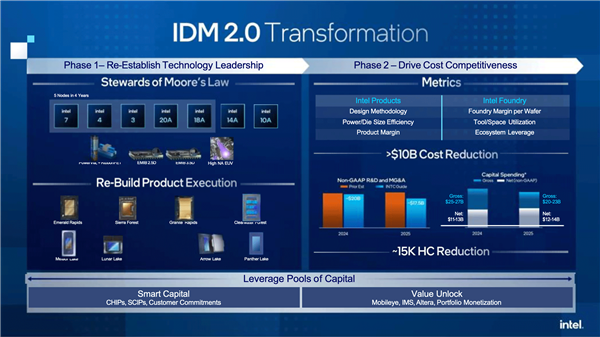

18A 공정을 사용하는 인텔의 첫 소비자 제품은 코어 Ultra 300 시리즈로 명명될 것으로 예상되는 Panther Lake가 될 것입니다. 첫 번째 데이터센터 제품은 시미즈 포레스트가 될 것이며 제온 7 시리즈로 명명될 것으로 예상됩니다. 두 제품 모두 양산에 들어가 2025년 출시될 예정입니다.

18A 공정은 인텔이 공정 기술에서 타이적전의 핵심 단계를 뛰어넘을 뿐 아니라 외부 세대 공장에 공급할 중요한 기회이기도 합니다.

인텔은 Microsoft 및 미국 국방부와 같은 잠재적인 파운드리 고객이 이미 관심을 가지고 있다고 밝혔습니다. 2025년 중으로 인텔 자체 제품과 외부 고객의 제품을 포함한 8개의 18A 칩이 완성될 것으로 예상됩니다.