IBM has unveiled its next-generation processor, the Telum II, designed for the new IBM Z mainframe, targeting mission-critical workloads and AI applications.

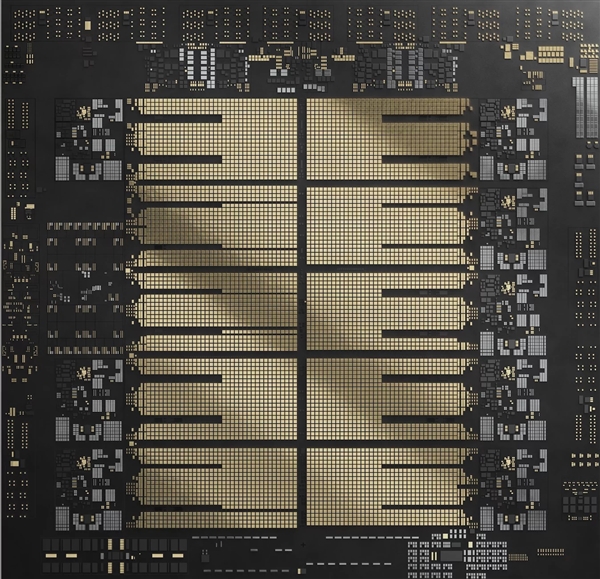

Manufactured using Samsung's 5HPP 5nm process, the Telum II features 43 billion transistors and integrates eight high-performance cores. It offers significant improvements in branch prediction, store write-back, and address translation.

Operating at a clock speed of 5.5GHz, the Telum II comes with 36MB of L2 cache (a 40% increase), 360MB of L3 cache, and 2.88GB of L4 cache - making it an IBM processor renowned for its extensive multi-level cache.

The processor boasts enhanced built-in AI accelerators with 24 TOPS of INT8 integer precision arithmetic, quadrupling the performance of its predecessor. It is optimized for low-latency, real-time AI workloads, enabling AI tasks to be handled by any core and delivering up to 192 TOPS of performance per chassis in a full configuration.

Initial Telum II Release

The original Telum was released in 2021.

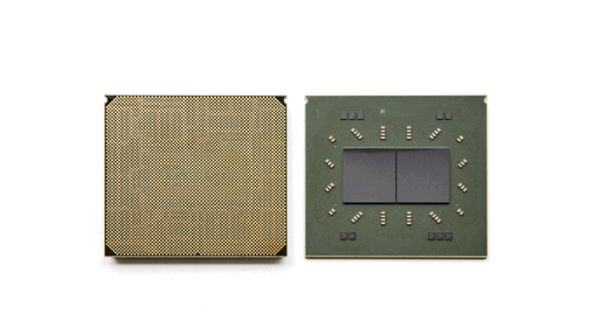

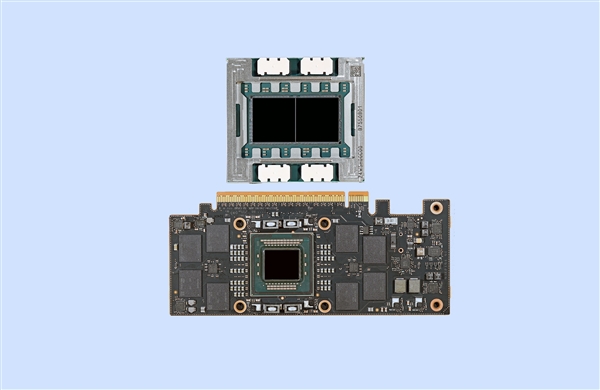

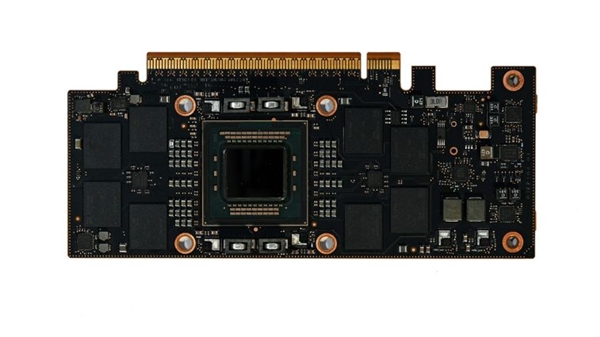

In conjunction with the Telum II, IBM also introduced the new Spyre AI accelerator card. Built on Samsung's 5LPE 5nm process, it comprises 26 billion transistors and includes 32 AI acceleration cores, architecturally similar to the AI accelerators in the Telum II. This card can interface with the IBM Z mainframe's IO subsystem via PCIe to provide additional AI acceleration.

Both the Telum II processor and Spyre accelerator card are expected to be available in 2025.

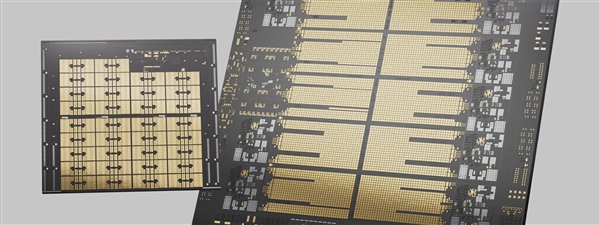

Telum II and Spyre accelerator card

Spyre accelerator card