TSMC는 인공지능(AI) 칩에 대한 전례 없는 수요를 경험하고 있으며, NVIDIA의 데이터센터 GPU에 대한 시장 수요도 크게 증가했습니다. 고객 주문을 충족하기 위해 새로운 시설 건설을 지속적으로 추진하고 있습니다. 병목 현상 중 하나는 CoWoS 패키징 용량으로, TSMC는 용량 확대와 더불어 새로운 패키징 기술을 적극적으로 모색하고 있습니다.

관련 언론 보도에 따르면 최근 업계 소식통은 TSMC가 기존의 원형 웨이퍼 대신 직사각형 기판을 사용하는 새로운 첨단 칩 패키징 기술을 개발하고 있다고 밝혔습니다. 이 혁신을 통해 단일 기판에 더 많은 칩을 배치할 수 있으므로 미래 AI 칩의 제조 요구 사항을 충족할 수 있습니다. 이 연구는 아직 초기 단계에 있으며 생산 준비까지는 몇 년이 걸릴 수 있지만, 이는 중요한 기술적 변화를 의미하며 TSMC를 다시 한 번 칩 제조 기술의 선두에 서게 할 것입니다.

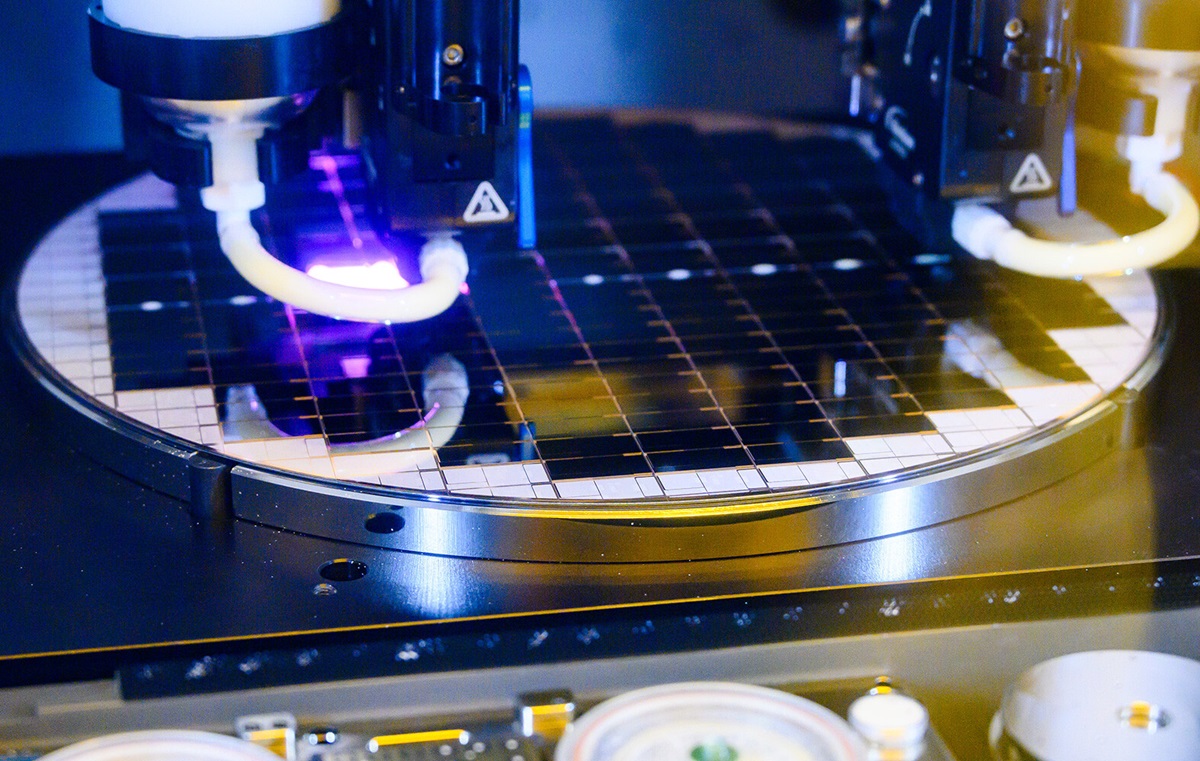

TSMC는 515mm x 510mm의 직사각형 기판 크기를 테스트하고 있는 것으로 알려져 있습니다. 현재 12인치(300mm) 웨이퍼와 비교하면 사용 가능한 면적이 3.7배 이상 커져 칩에 대한 시장 수요를 더 잘 충족할 수 있습니다. 또한 직사각형 기판을 사용하면 원형 웨이퍼의 가장자리에 있는 불완전한 칩을 더 잘 제거할 수 있습니다. 웨이퍼의 모양만 바뀐 것처럼 보일 수 있지만 실제로는 전체 제조 공정을 완전히 개편해야 합니다.

TSMC는 패널 레벨 패키징 기술을 포함한 첨단 패키징 기술의 발전과 발전을 면밀히 모니터링하고 있다고 언론 보도에 답변했습니다.