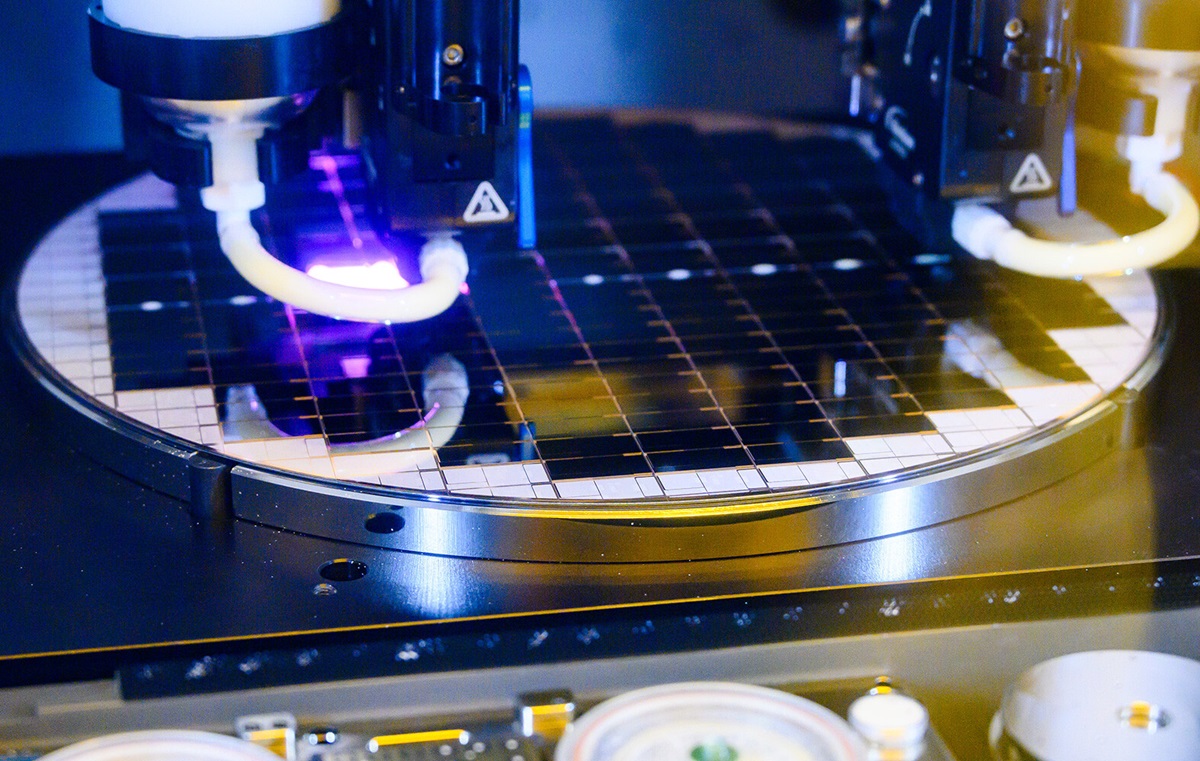

TSMCは人工知能(AI)チップに対するかつてない需要に見舞われており、エヌビディアのデータセンター向けGPUの市場需要も大幅に増加しています。顧客からの注文に応えるため、TSMCは新たな設備の建設を継続的に目指しています。現在のボトルネックの1つはCoWoSパッケージング能力であり、TSMCは能力拡張に加えて新しいパッケージング技術を積極的に模索しています。

関連メディアの報道によると、業界筋は最近、TSMCが従来の丸いウェハーの代わりに長方形の基板を使用する新しい先進的なチップパッケージング技術を開発していることを明らかにしました。この技術革新により、1枚の基板により多くのチップを搭載できるようになり、将来のAIチップの製造ニーズに対応できるようになります。この研究はまだ初期段階にあり、生産準備には数年かかるかもしれませんが、これは重要な技術的転換を意味し、TSMCをチップ製造技術の最前線に再び位置づけることになるでしょう。

TSMCは515mm×510mmの長方形の基板サイズをテストしていることが分かっています。現在の12インチ(300mm)ウェハーと比較して、利用可能な面積は3.7倍以上となり、チップに対する市場の需要をより満たすことが可能です。また、長方形の基板を使用することで、丸いウェハーの端にある不完全なチップをより排除することができます。ウェハーの形状だけが変わったように見えるかもしれませんが、実際には製造プロセス全体を全面的に見直す必要があります。

TSMCはメディアの報道に対し、パネルレベル・パッケージング技術を含む先進パッケージング技術の進歩や発展を注意深く見守っていると述べました。